Yet since a drawn wire in the layout editor is a perfectly ideal that doesn't show the reality of the physical chip geometries. This is done by tools such as Cadence Encounter or Synopsys tools. Layout engineers are sometimes called physical designers since a lot of layout is generated by the machine in digital blocks.

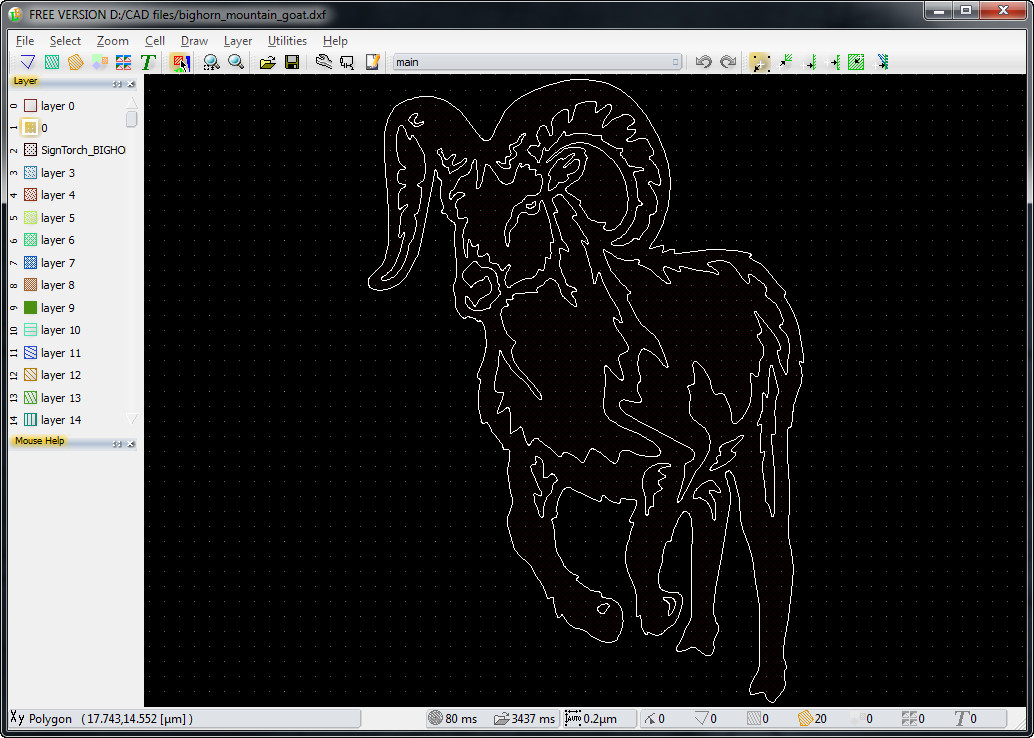

Layout Editors have started to incorporate other tools to see parasitics since RF and smaller geometries have been introduced. Layout Editors have grown in complexity and function to deal with the ever growing device count and issues that weren't issues before when device counts were smaller and geometries were much larger. Layout editors have moved mostly to the server world through the likes of Cadence Virtuoso and Mentor though some is still done through PC tools through tools such as L-Edit but sadly there is little choose from in the PC market though there are a few exceptions such as Magic and Klayout but these are mostly utilized for utility such as to view GDS files not fully powered layout editors as there once was in the 90's. Other layout editors use large track ball like device with clickers. In the 80's and 90's quite a bit of layout editing was done on personal pc's using such tools as IC Editors, L-Edit and others. The advent of computers particularly mainframes and mini computers helped bring layout to the digital world of computers. Layout used to be done on sticks and yards of strings for very basic components. Boolean generation is quite often done in the layout editor. Other checks include ESD, XOR, EOS and verification with the foundry called Mebes check to ensure the boolean algorithms that generate the mask layers are done as intended. Other tools in include field solver verification to check for important specs such as device resistance and sources of problems such as electromigration or too thin wires resulting in burn up of wires causing shorts or open circuits. The layout engineer uses DRC and LVS checks to ensure that the circuit is both manufacturable and functional. The layout engineer uses metal routing and other layers at times to connect all of the components, again taking care to avoid unwanted layout parasitics.

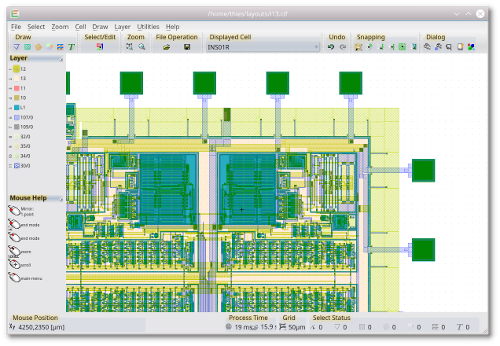

The layout engineer positions the components to minimize both the area required and the negative effects of layout parasitics upon the circuit performance and also to allow efficient routing to components. Either the tool or the layout engineer creates a physical view of the circuit including all of the required components, wires, layers and pads. The layout engineer receives the schematic from the designer in electrical form 2. The typical flow for the layout of analog circuits might be :ġ. Software of this type is similar to computer aided drafting software, but is specialized for the task of integrated circuit layout. Typically the view will include the components (usually as pcells), metal routing tracks, vias and electrical pins. Software used in integrated circuit designĪn Integrated circuit layout editor or IC layout editor is an electronic design automation software tool that allows a user to digitize the shapes and patterns that form an integrated circuit.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed